Фрагмент перевода 4 главы «PAGING» руководства “Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 3 (3A & 3B):System Programming Guide”

Другие главы

Глава 3 объясняет как сегментация преобразует логические адреса в линейные адреса. Страничный механизм (или трансляция линейных адресов) — процесс преобразования линейных адресов, так что они могут быть использованы для доступа к памяти или устройствам ввода-вывода. Страничный механизм транслирует каждый линейный адрес в физический адрес и определяет, для каждой трансляции, какой доступ к линейным адресам позволен (the address’s access rights) и тип кеширования используемый для таких адресов (the address’s memory type).

Intel-64 процессоры поддерживают три различных страничных механизма. Эти режимы идентифицируются и определяются в разделе 4.1. Раздел 4.2 дает обзор механизма трансляции используемого во всех режимах. Разделы 4.3, 4.4 и 4.5 описывают три страничных механизма детально.

Раздел 4.6 описывает как страничный механизм определяет и использует права доступа. Раздел 4.7 обсуждает исключения которые могут быть сгенерированы страничным механизмом (page-fault exceptions). Раздел 4.8 описывает данные, которые процессор записывает в ответ на доступ к линейным адресам (accessed and dirty flags).

Раздел 4.9 описывает как страничный механизм определяет типы памяти используемые для доступа к линейным адресам. Раздел 4.10 детализирует кеширование процессором информации о трансляции адресов (linear-address translation). Раздел 4.11 описывает взаимодействие страничного механизма с различными VMX функциями. Раздел 4.12 дает обзор как страничный механизм может использоваться для реализации виртуальной памяти.

Режимы страничных механизмов и управляющие биты.

4.1 PAGING MODES AND CONTROL BITS

Страничный механизм контролируется следующими битами:

Paging behavior is controlled by the following control bits:

- Флаги WP и PG управляющего регистра CR0 (биты 16 и бит 31 соотвественно).

- Флаги PSE, PAE, PGE и PCIDE в управляющем регистре CR4 (бит 4, 5, 7 и 17).

- Флаги LME и NXE в IA32_EFER MSR (бит 8 и биты 11, соотвественно).

Программное обеспечение включает страничный механизм с помощью инструкции записи MOV в регистр CR0, для установки флага CR0.PG. Прежде чем делать это, программное обеспечение должно убедиться, что контрольный регистр CR3 содержит физический адрес первой страничной структуры, который процессор будет использовать для линейной адресной трансляции (linear-address translation см. Section 4.2) и что эта структура инициализирована как необходимо. См. таблицы 4-3, 4-7 и 4-12 для описания использования CR3 при различных режимах страничного механизма.

Раздел 4.1.1 определяет как значения CR0.PG, CR4.PAE и IA32_EFER.LME определяют включен ли страничный механизм и если включен, какие из 3-х страничных режимов используются. Раздел 4.1.2 объясняет как настраивать эти биты для установки или изменения страничных режимов. Раздел 4.1.3 обсуждает как CR0.WP, CR4.PSE, CR4.PGE, CR4.PCIDE, и IA32_EFER.NXE флаги влияют на работу в различных режимах трансляции адресов.

4.1.1 Three Paging Modes

Если флаг CR0.PG = 0, страничный механизм выключен. Логический процессор рассматривает все линейные адреса как физические. Флаги CR4.PAE и IA32_EFER.LME игнорируются процессором, также как CR0.WP, CR4.PSE, CR4.PGE и IA32_EFER.NXE.

Страничный механизм включен, если CR0.PG = 1. Страничный механизм может быть включен только если защита включена (CR0.PE = 1). Если страничный механизм включен, один из 3-х режимов страничных режимов используется. Значения CR4.PAE и IA32_EFER.LME определяют какой страничный режим используется:

- Если CR0.PG = 1 и CR4.PAE = 0, 32-битный страничный механизм используется. 32-битный страничный механизм описывается в разделе 4.3. 32-битный страничный механизм использует флаги CR0.WP, CR4.PSE и CR4.PGE как описано в разделе 4.1.3.

- Если CR0.PG = 1, CR4.PAE = 1 и IA32_EFER.LME = 0, PAE режим трансляции используется. PAE страничный режим описан в разделе 4.4. PAE режим использует CR0.WP, CR4.PGE и IA32_EFER.NXE как описано в разделе 4.1.3.

- Если CR0.PG = 1, CR4.PAE = 1 и IA32_EFER.LME = 1, IA-32e страничный механизм включен. IA-32e страничный режим описан в разделе 4.5. IA-32e страничный режим использует CR0.WP, CR4.PGE, CR4.PCIDE и IA32_EFER.NXE как описано в разделе 4.1.3. IA-32e страничный режим доступен только для процессоров, поддерживающих Intel 64 архитектуру.

Флаг LMA в регистре IA32_EFER MSR (бит 10) является битом состояния указывающим находится ли процессор в режиме IA-32e (и т.о. используется ли IA-32e страничный режим). Процессор всегда устанавливает IA32_EFER.LMA = CR0.PG & IA32_EFER.LME. Программное обеспечение не может прямо модифицировать IA32_EFER.LMA; При применении WRMSR к регистру IA32_EFER MSR бит 10 игнорируется вне зависимости от значения указанного операнда

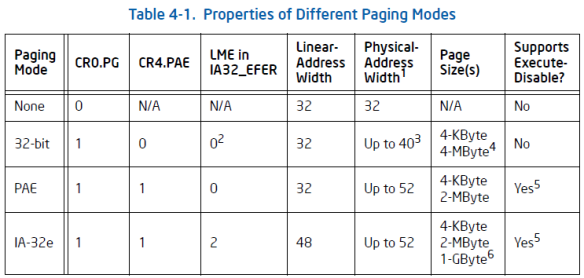

Три режима трансляции отличаются следующими деталями:

- Размер линейного адреса. Диапозон линейных адресов, которые могут быть транслированы.

- Размер физического адреса. Число бит физических адресов производимых механизмом трансляции.

- Размером страницы. Granularity (шаг) с которым линейные адреса транслируются. Линейные адреса на одной странице транслируются на соответствующие физические адреса на одной физической странице.

- Поддержка для запрета выполнения. В некоторых режимах трансляции, программное обеспечение может быть обезопашено от загрузки инструкций со страниц которые для других нужд являются доступными для чтения.

(Иллюстрация из руководства Intel)

Таблица 4-1 иллюстрирует ключевые отличия между тремя режимами страничного механизма.

Замечания

- Число бит физического адреса всегда ограничено значением MAXPHYADDR; см. раздел 4.1.4.

- Процессор следит за тем, чтобы IA32_EFER.LME было 0 если CR0.PG = 1 и CR4.PAE = 0.

- В 32-битном режиме страничный механизм поддерживает физические адреса большие чем 32 бит только для 4 мегабайтных страниц и только если механизм PSE-36 поддерживается; см. разделы 4.1.4 и 4.3

- 4-MByte страницы используются с 32-битным страничным режимом только если CR4.PSE = 1; см. раздел 4.3.

- Права доступа «запрет выполнения» (Execute-disable) применяются только если IA32_EFER.NXE = 1; см. раздел 4.6.

- Не все процессоры, поддерживающие IA-32e, поддерживают 1-GByte страницы; см. раздел 4.1.4.

Поскольку они используются только если IA32_EFER.LME = 0, 32-битный страничный режим и PAE режимы используются только в стандартном защищенном режиме. Поскольку стандартный защищенный режим не может генерировать линейных адресов больших 32-бит, 32-битный страничный режим и PAE страничный режим транслируют 32-битные линейные адреса.

Поскольку он используется только если IA32_EFER.LME = 1, IA-32e страничный режим используется только в IA-32e режиме. Фактически, использование IA-32e страничного режима и задает IA-32е режим. Режим IA-32e имеет 2 подрежима:

- Режим совместимости. Этот режим использует 32-битные линейные адреса. IA-32e режим трансляции рассматривает биты c 32 по 47 таких адресов как все 0.

- 64-битный режим. Хотя этот режим выдает 64-битные линейные адреса, процессор контролирует что биты с 47 по 63 таких адресов идентичны. IA-32е страничный механизм не использует биты c 48 по 63 таких адресов.

Такой адрес называется каноническим. Использование не-канонических линейных адресов в 64-битном режиме приводит к генерации general-protection exception (#GP(0)); Процессор не пытается транслировать не-канонические линейные адреса используя IA-32е страничный механизм.

4.1.2 Paging-Mode Enabling

Если CR0.PG = 1, логический процессор находится в одном из трех страничных режимов, в зависимости от значений CR4.PAE и IA32_EFER.LME=1. Рисунок 4-1 иллюстрирует как программное обеспечение может включать страничные режимы и делать переходы между ними. Ниже описываются сущности приведенные на картинке, ограничения и другие детали.

- IA32_EFER.LME не может быть изменен, если страничный механизм уже включен (CR0.PG = 1). Попытка его модификации с использованием WRMSR вызывает general-protection исключение(#GP(0)).

- Страничный механизм не может быть включен (установкой CR0.PG в 1) пока CR4.PAE = 0 и IA32_EFER.LME = Попытка сделать это с использованием MOV в CR0 вызывает general protection исключение (#GP(0)).

- CR4.PAE не может быть сброшен, пока IA-32e страничный механизм активен (CR0.PG = 1 и IA32_EFER.LME = 1). Попытка сделать это с помощью MOV в CR4 вызывает general protection исключение (#GP(0)).

- Не зависимо от текущего страничного режима, программное обеспечение может выключить страничный механизм сбросом CR0.PG с помощью MOV в CR0.1

Если CR4.PCIDE = 1, попытка сбросить CR0.PG вызывает general-protection исключение (#GP); программное обеспечение должно сбросить CR4.PCIDE прежде, чем пытаться выключить страничный механизм.

- Программное обеспечение может переходить между 32-битным страничным режимом и PAE режимом изменением значение флага CR4.PAE с помощью MOV в CR4.

- Программное обеспечение не может делать прямые переходы в другие режимы из режима IA-32e. Страничный режим должен быть предварительно выключен (сбросом флага CR0.PG c помощью MOV в CR0), затем установить CR4.PAE и IA32_EFER.LME в нужные значения (с помощью MOV в CR4 и WRMSR), и затем включить страничный механизм вновь (установкой CR0.PG с помошью MOV в CR0). Как было замечено ранее, попытка сброса либо CR4.PAE либо IA32_EFER.LME в IA-32е режиме вызывает general-protection исключение (#GP(0)).

- VMX переходы (transitions) позволяют переходы между страничными режимами не возможные с помощью обычных MOV в CR или WRMSR. Это благодаря тому, что VMX переходы могут загружать CR0, CR4 и IA32_EFER одной операцией. См. раздел 4.11.1.

Титанический труд 🙂